UNIVERSIDADE DE SANTIAGO DE COMPOSTELA

Departamento de Electrónica e Computación

PhD Thesis

## DYNAMICALLY RECONFIGURABLE ARCHITECTURE FOR EMBEDDED COMPUTER VISION SYSTEMS

Author:

Alejandro Manuel Nieto Lareo

PhD supervisors:

David López Vilariño Víctor Manuel Brea Sánchez

Santiago de Compostela, September 2012

**Dr. David López Vilariño**, Profesor Titular de Universidade da Área de Electrónica da Universidade de Santiago de Compostela

**Dr. Víctor Manuel Brea Sánchez**, Profesor Contratado Doutor da Área de Electrónica da Universidade de Santiago de Compostela

#### FAN CONSTAR:

Que a memoria titulada **DYNAMICALLY RECONFIGURABLE ARCHITECTURE FOR EM-BEDDED COMPUTER VISION SYSTEMS** foi realizada por **D. Alejandro Manuel Nieto Lareo** baixo a nosa dirección no Departamento de Electrónica e Computación e no Centro Singular de Investigación en Tecnoloxías da Información (CITIUS) da Universidade de Santiago de Compostela, e constitúe a Tese que se presenta para optar ao grado de Doutor.

Santiago de Compostela, setembro de 2012

David López Vilariño Codirector da tese Víctor Manuel Brea Sáncez Codirector da tese

**Doutorando** Alejandro Manuel Nieto Lareo

Aos meus pais e ao meu irmán, pero sobre todo, aos meus avós.

Don't worry head, the computer will do our thinking now! Homer J. Simpson (after buying one)

People who are really serious about software should make their own hardware.

Alan Kay

## Acknowledgements

It is a pleasure to thank the many people who made this thesis possible.

It is difficult to overstate my gratitude to my PhD. supervisors, Dr. David López Vilariño and Dr. Víctor Manuel Brea Sánchez. With their enthusiasm, their inspiration, and their great efforts to explain things clearly and simply, they helped to make research fun for me. Throughout all my thesis period, they provided encouragement, sound advice, good teaching, good company, and lots of good ideas. I would have been lost without them.

I wish to express my warm and sincere thanks to Associate Professor Javier Díaz Alonso from the Universidad de Granada, and Professor Nigel Topham from the University of Edinburgh, who not only allowed me to improve the results of this work and expand the initial objectives, but also they have given me the opportunity to work with leading research groups and have allowed me to enjoy new experiences.

My sincere thanks to Professor Diego Cabello Ferrer, Associate Professor Paula López Martínez and Dr. Fernando Rafael Pardo Seco from the Universidade de Santiago de Compostela, Associate Professor Roberto Rodríguez Osorio from the Universidade da Coruña and Dr. Carmen Alonso Montes, for all the help they rendered me during my research period. I also wish to thank Dr. Jordi Albó Canals from the Universitat Ramon Llull, Dr. Freddie Qu and Christopher Thompson from the University of Edinburgh, and all members of the Departamento de Arquitectura y Tecnología de Computadores of the Universidad de Granada, for they support during my research stays. My gratitude is also extended to all members of the Departamento de Electrónica e Computación of the University of Santiago de Compostela, and in particular to the Grupo de Visión Artificial.

I am indebted to my many colleagues for providing a stimulating and fun environment in which to learn and grow. I am especially grateful to David, Bea B., Bea P., Roi, Fernando, Levo, Natalia, Manuel, Cris, Yago, Pablo, María and Juan at the Departamento de Electrónica

e Computación of the Universidade de Santiago de Compostela, for all the emotional support, comraderie, entertainment, and caring they provided. I also wish to thank Xabier, Lorena, Mar, Isa, Raquel, Paloma, Ana, Yolanda and many others who have been there all these years. I also want make special mention to the people of the Banda de Música de Arca, because work is not everything. And in general, to all those who in one way or another have been there all these years.

Tamén quero agradecer á Xunta de Galicia a creación do Programa María Barbeito, así como aos proxectos PGIDT06TIC10502PR, 10PXIB206168PR e 10PXIB206037PR, que me permitiron financiar esta tese e gozar da experiencia de colaborar con outros grupos de investigación, algo moi importante para a consecución dos meus obxectivos.

Finalmente, e o máis importante, quero darlle as gracias aos meus pais, M<sup>a</sup> Obdulia e Manuel, ao meu irmán Adrián, e aos meus avós Secundino e Obdulia. Eles déronme todo o apoio que precisei estes anos non so para acabar este traballo senón para medrar como persoa. A eles lles dedico esta tese.

Santiago de Compostela, September 2012

# Contents

| Resumo da tese |                                |                                        |                              |    |  |  |  |  |

|----------------|--------------------------------|----------------------------------------|------------------------------|----|--|--|--|--|

| Introduction   |                                |                                        |                              |    |  |  |  |  |

|                | Mot                            | ivation a                              | and objectives               | 11 |  |  |  |  |

|                | Con                            | tributior                              | 18                           | 12 |  |  |  |  |

|                | Outl                           | ine .                                  |                              | 14 |  |  |  |  |

| 1              | Bac                            | kground                                | d and related work           | 17 |  |  |  |  |

|                | 1.1                            | The ch                                 | nallenges of Computer Vision | 19 |  |  |  |  |

|                |                                | 1.1.1                                  | Low-level vision             | 19 |  |  |  |  |

|                |                                | 1.1.2                                  | Mid-level vision             | 21 |  |  |  |  |

|                |                                | 1.1.3                                  | High-level vision            | 22 |  |  |  |  |

|                | 1.2                            | Comp                                   | uting platforms              | 23 |  |  |  |  |

|                |                                | 1.2.1                                  | Computing paradigms          | 23 |  |  |  |  |

|                |                                | 1.2.2                                  | Current devices              | 27 |  |  |  |  |

|                |                                | 1.2.3                                  | Discussion                   | 33 |  |  |  |  |

|                | 1.3                            | Relate                                 | d work                       | 39 |  |  |  |  |

|                | 1.4                            | Summ                                   | ary                          | 45 |  |  |  |  |

| 2              | Addressing the low-level stage |                                        |                              |    |  |  |  |  |

|                | 2.1                            | Evaluating fine-grain processor arrays |                              |    |  |  |  |  |

|                |                                | 2.1.1                                  | Processor architecture       | 48 |  |  |  |  |

|                |                                | 2.1.2                                  | Hardware implementation      | 53 |  |  |  |  |

|                |                                | 2.1.3                                  | Algorithm evaluation         | 55 |  |  |  |  |

|                |                                | 2.1.4                                  | Discussion                   | 65 |  |  |  |  |

## Contents

|   | 2.2               | Genera                                                                                                               | al-purpose coarse-grain processor array                                                                                                                                                                                                                                                                                          | 8                                                        |  |  |

|---|-------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

|   |                   | 2.2.1                                                                                                                | Instruction Set                                                                                                                                                                                                                                                                                                                  | 8                                                        |  |  |

|   |                   | 2.2.2                                                                                                                | Processor Architecture                                                                                                                                                                                                                                                                                                           | 9                                                        |  |  |

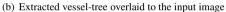

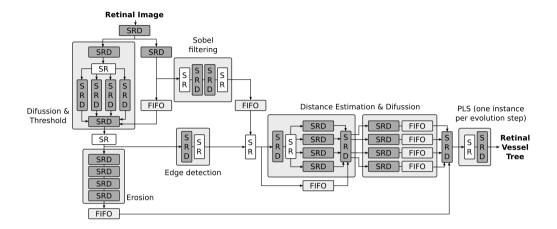

|   | 2.3               | Case o                                                                                                               | f study: retinal vessel-tree extraction                                                                                                                                                                                                                                                                                          | 5                                                        |  |  |

|   |                   | 2.3.1                                                                                                                | Algorithm execution flow                                                                                                                                                                                                                                                                                                         | 8                                                        |  |  |

|   |                   | 2.3.2                                                                                                                | Pixel-Level Snakes                                                                                                                                                                                                                                                                                                               | 9                                                        |  |  |

|   |                   | 2.3.3                                                                                                                | Performance remarks                                                                                                                                                                                                                                                                                                              | 3                                                        |  |  |

|   | 2.4               | Performance evaluation                                                                                               |                                                                                                                                                                                                                                                                                                                                  |                                                          |  |  |

|   |                   | 2.4.1                                                                                                                | FPGA prototyping and validation 8                                                                                                                                                                                                                                                                                                | 5                                                        |  |  |

|   |                   | 2.4.2                                                                                                                | Algorithm evaluation                                                                                                                                                                                                                                                                                                             | 6                                                        |  |  |

|   |                   | 2.4.3                                                                                                                | Architectural improvements                                                                                                                                                                                                                                                                                                       | 7                                                        |  |  |

|   | 2.5               | Compa                                                                                                                | arison with other approaches                                                                                                                                                                                                                                                                                                     | 8                                                        |  |  |

|   |                   | 2.5.1                                                                                                                | Pixel-Parallel Processor Arrays                                                                                                                                                                                                                                                                                                  | 0                                                        |  |  |

|   |                   | 2.5.2                                                                                                                | Massively Parallel Processor Arrays                                                                                                                                                                                                                                                                                              | 3                                                        |  |  |

|   |                   | 2.5.3                                                                                                                | Results and comparison                                                                                                                                                                                                                                                                                                           | 8                                                        |  |  |

|   | 2.6               | Summ                                                                                                                 | ary                                                                                                                                                                                                                                                                                                                              | 4                                                        |  |  |

|   |                   |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                  |                                                          |  |  |

| 3 | Expa              | anding                                                                                                               | the range of operation 10                                                                                                                                                                                                                                                                                                        | 7                                                        |  |  |

| 3 | <b>Exp</b><br>3.1 | -                                                                                                                    | the range of operation     10'       sor architecture     10'                                                                                                                                                                                                                                                                    |                                                          |  |  |

| 3 | _                 | -                                                                                                                    |                                                                                                                                                                                                                                                                                                                                  | 8                                                        |  |  |

| 3 | _                 | Proces                                                                                                               | sor architecture                                                                                                                                                                                                                                                                                                                 | 8<br>8                                                   |  |  |

| 3 | _                 | Proces 3.1.1                                                                                                         | sor architecture    100      Processor datapath    100                                                                                                                                                                                                                                                                           | 8<br>8<br>3                                              |  |  |

| 3 | _                 | Proces<br>3.1.1<br>3.1.2<br>3.1.3                                                                                    | sor architecture    100      Processor datapath    100      Operation modes    111                                                                                                                                                                                                                                               | 8<br>8<br>3<br>0                                         |  |  |

| 3 | 3.1               | Proces<br>3.1.1<br>3.1.2<br>3.1.3                                                                                    | sor architecture    100      Processor datapath    100      Operation modes    111      Instruction set    120                                                                                                                                                                                                                   | 8<br>8<br>3<br>0<br>3                                    |  |  |

| 3 | 3.1               | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform                                                                         | sor architecture    100      Processor datapath    100      Operation modes    111      Instruction set    120      mance evaluation    122                                                                                                                                                                                      | 8<br>8<br>3<br>0<br>3<br>3                               |  |  |

| 3 | 3.1               | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1                                                                | sor architecture    100      Processor datapath    100      Operation modes    111      Instruction set    120      mance evaluation    122      FPGA prototyping and validation    122                                                                                                                                          | 8<br>8<br>3<br>0<br>3<br>3<br>5                          |  |  |

| 3 | 3.1               | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3                                              | sor architecture    100      Processor datapath    100      Operation modes    111      Instruction set    120      mance evaluation    122      FPGA prototyping and validation    122      Algorithm evaluation    122                                                                                                         | 8<br>3<br>0<br>3<br>5<br>2                               |  |  |

| 3 | 3.1<br>3.2        | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3                                              | sor architecture       100         Processor datapath       100         Operation modes       111         Instruction set       112         mance evaluation       122         FPGA prototyping and validation       122         Algorithm evaluation       122         Case of study: feature extraction and matching       132 | 8<br>3<br>0<br>3<br>5<br>2<br>0                          |  |  |

| 3 | 3.1<br>3.2        | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3<br>Compa                                     | sor architecture100Processor datapath100Operation modes111Instruction set120mance evaluation122FPGA prototyping and validation122Algorithm evaluation122Case of study: feature extraction and matching132arison with other approaches140                                                                                         | 8<br>8<br>3<br>0<br>3<br>5<br>2<br>0<br>0                |  |  |

| 3 | 3.1<br>3.2        | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3<br>Compa<br>3.3.1                            | sor architecture100Processor datapath100Operation modes111Instruction set120mance evaluation121FPGA prototyping and validation122Algorithm evaluation122Case of study: feature extraction and matching132arison with other approaches140General-purpose coarse-grain processor array140                                          | 8<br>8<br>3<br>0<br>3<br>3<br>5<br>2<br>0<br>0<br>2      |  |  |

| 3 | 3.1<br>3.2        | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3<br>Compa<br>3.3.1<br>3.3.2                   | sor architecture100Processor datapath100Operation modes111Instruction set121mance evaluation122FPGA prototyping and validation122Algorithm evaluation122Case of study: feature extraction and matching132arison with other approaches144SCAMP-3 Vision Chip144                                                                   | 8<br>3<br>0<br>3<br>5<br>2<br>0<br>0<br>2<br>3           |  |  |

| 3 | 3.1<br>3.2        | Proces<br>3.1.1<br>3.1.2<br>3.1.3<br>Perform<br>3.2.1<br>3.2.2<br>3.2.3<br>Compa<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | sor architecture100Processor datapath100Operation modes111Instruction set120mance evaluation121FPGA prototyping and validation122Algorithm evaluation122Case of study: feature extraction and matching132arison with other approaches144General-purpose coarse-grain processor array144SCAMP-3 Vision Chip144Ambric Am2045144    | 8<br>8<br>3<br>0<br>3<br>5<br>2<br>0<br>0<br>2<br>3<br>4 |  |  |

## Conclusions

xii

| Contents                                     |     |  |

|----------------------------------------------|-----|--|

| A SIMD/MIMD Hybrid Processor timing diagrams | 155 |  |

| List of acronyms                             | 161 |  |

| Bibliography                                 | 163 |  |

| List of Figures                              | 183 |  |

| List of Tables                               | 185 |  |

Seguindo o regulamento dos estudios de terceiro ciclo da Universidade de Santiago de Compostela, aprobado na Xunta de Goberno do día 7 de abril de 2000 (DOG de 6 de marzo de 2001) e modificado pola Xunta de Goberno de 14 de novembro de 2000, o Consello de Goberno de 22 de novembro de 2003, de 18 de xullo de 2005 (artigos 30 a 45), de 11 de novembro de 2008 e de 14 de maio de 2009; e, concretamente, cumprindo coas especificacións indicadas no capítulo 4, artigo 30, apartado 3 de dito regulamento, amósase a continuación un resumo en galego da presente tese.

## Motivación e obxectivos

Os algoritmos e técnicas de Visión por Computador son cada vez máis robustos e precisos, ofrecendo novas posibilidades para o tratamento da información visual. Sen embargo, isto implica un aumento dos requisitos de cómputo polo que a súa implementación en dispositivos máis aló do alcance dos prototipos está a voltarse máis complexo. Son precisos novos enfoques que non afecten ás características dos algoritmos para acadar solucións de compromiso en termos de velocidade, latencia, consumo de potencia ou custo. Isto inclúe tanto ao apartado do software como ao da arquitectura hardware para poder aproveitar eficientemente as características do dispositivo e explotar plenamente as capacidades dos algoritmos.

Para solventar un problema no ámbito da Visión por Computador existen moitas técnicas e aproximacións dispoñibles na literatura. A variedade de algoritmos é moi ampla e presentan características moi diferentes, incluíndo non so a representación de datos ou as operacións aritméticas, se non tamén os paradigmas de computación ou a complexidade dos programas. Isto fai que o deseño das arquitecturas hardware sexa un desafío se é a mesma arquitectura a que ten que afrontar algoritmos diferentes cumprindo unhas restricións estritas.

Os ordenadores de escritorio son a miúdo empregados para desenvolver os algoritmos. Ofrecen unha gran flexibilidade para executar calquera algoritmo e avaliar a súa viabilidade e precisión. Con todo, o dispositivo obxectivo depende da aplicación e adoitan empregarse módulos adicionais para acelerar o proceso. Para cumprir os requisitos da aplicación pode ser incluso necesario deseñar unha arquitectura específica. Neste caso é posible optimizar todas as figuras de mérito implicadas. Os diferentes campos de aplicación fixan diferentes requisitos polo que as distintas arquitecturas deben adaptarse aos mesmos de forma eficaz.

Os avances na industria do semicondutor permiten incluír cada vez máis recursos na mesma unidade de área, mantendo un consumo de potencia contido. Isto fixo posible desenvolver novos sistemas embebidos cun rendemento similar aos sistemas convencionais do pasado recente. Deste xeito, as novas aplicacións son tecnicamente factibles e o mercado de aplicacións de visión embebidos está aumentando significativamente. Os sistemas nun chip posibilitan embeber no mesmo chip todos os módulos necesarios para un sistema dado, incluíndo computación, control e comunicacións, proporcionando unha vantaxe significativa sobre o seu equivalente sistema multi-chip. Sen embargo, os sistemas nun chip requiren un longo período de deseño e moitos recursos, tanto humanos como materiais. Ademais, as arquitecturas a medida tamén requiren un período de adestramento polos enxeñeiros de software para explotar plenamente as súas capacidades, reducíndose así a vantaxe competitiva destes sistemas. Isto é crítico cando medra o número de unidades de propósito específico que executan os diferentes algoritmos empregados.

O obxectivo deste traballo é proporcionar unha arquitectura capaz de executar a maioría dos algoritmos de Visión por Computador cun rendemento adaptable ás distintas etapas de cada algoritmo. Ademais, ten que ser capaz de executar as etapas restantes de xeito que o rendemento global non se vexa comprometido. A arquitectura tamén está pensada para reducir o tempo empregado en migrar os algoritmos, reducindo a etapa de migración facilitando a paralelización e a sincronización entre os diferentes bloques concurrentes do algoritmo. Desde o punto de vista da flexibilidade, o sistema ten que ser modular e escalable para afrontar diferentes áreas de mercado con diferentes requisitos, como rendemento, consumo de área ou custo. As melloras na arquitectura ou as modificacións baixo demanda deben ser posible sen mudar dramaticamente a forma en que o hardware traballa. Todos estes elementos combinados proporcionarán suficiente flexibilidade e rendemento para executar eficientemente a maior

Esta tese está dividida en tres capítulos. O Capítulo 1 presenta os desafíos da Visión por Computador, incluíndo os diferentes paradigmas de computación e as arquitecturas hardware e dispositivos empregados para afrontar os requisitos dos algoritmos. No Capítulo 2 preséntase unha nova arquitectura hardware para executar algoritmos de visión temperá. Despois de examinar diferentes aproximacións, estudiaranse as capacidades dun procesador masivamente paralelo para o procesamento de imaxes binarias. As conclusións deste estudio son esenciais para o deseño dunha arquitectura máis eficiente e capaz para tarefas de visión temperá. Testearase empregando un algoritmo usado en aplicacións médicas, altamente custoso en termos computacionais. No Capítulo 3, os resultados obtidos da comparativa do procesador de propósito xeral descrito no capítulo anterior son empregados para definir unha nova arquitectura. Esta arquitectura está deseñada para aplicacións embebidas e enfocada na reconfiguración dinámica do seu camiño de datos para reproducir o fluxo de execución do algoritmo en execución. Deste xeito, a arquitectura aumenta o seu rango de operación de modo que todas as etapas dun algoritmo de Visión de Computador xenérico poden ser implementadas de xeito eficiente nun único dispositivo embebido. Os resultados da execución de diversos algoritmos de procesado de imaxe e a comparativa con outras solucións similares completan este capítulo. Finalmente, extráense as principais conclusións deste traballo.

## Introdución

A gran variedade de aplicacións de Visión por Computador fai difícil clasificalas en categorías claramente diferenciadas. Como resultado, o deseño dunha única arquitectura hardware que execute eficientemente todas as etapas de procesado que inclúe calquera algoritmo de Visión por Computador convértese nunha tarefa moi complexa. Na literatura están dispoñibles diversos estudios onde diferentes plataformas son testeadas baixo as mesmas condicións. Estes estudios amosan que o axuste fino dos parámetros é crítico en termos de rendemento e que o deseño de novas técnicas de computación paralela é un requisito para explorar as capacidades dos dispositivos que inclúen máis dunha unidade de cómputo. Ademais, o aumento das vendas e a aparición de mercados emerxentes fai que os investimentos en novo hardware sexa unha necesidade.

A plataforma máis accesible é un computador persoal equipado cunha GPU con soporte para cómputo de propósito xeral. Tanto como plataforma de deseño como dispositivo final, o computador persoal reduce enormemente o tempo de desenvolvemento e os custos asociados.

As GPUs ofrecen un alto rendemento nas tarefas máis intensivas mentres que as CPUs ofrecen extensións multimedia que permiten acelerar o cómputo nas etapas nas que non é posible empregar ás GPUs. Ademais, inclúen todos os elementos necesarios para comunicacións, almacenamento e interacción co usuario. A dispoñibilidade de modelos é moi grande polo que é posible seleccionar a plataforma máis adecuada segundo para cada aplicación, cumprindo así os seus requisitos. Cando o rendemento da CPU non é adecuado, os DSPs son unha seria alternativa. Ademais, o seu uso é case obrigatorio cando estamos a falar de sistemas embebidos e non queremos comprometer o rendemento, e onde o consumo de potencia ou o factor de forma son moi restritivos. Son amplamente utilizados para prototipar chips de aplicación específica aínda que as FPGAs reduciron o seu nicho de mercado. Os FPGAs ofrecen unha alta integración e flexibilidade ademais dun grande número de unidades xa dispoñibles que permiten reducir os custos asociados ao deseño, desenvolvemento e testeo. A pesar de que todos os dispositivos descritos son de aplicación específica, non foron concibidos para unha aplicación única. Para reducir os custos, os fabricantes expanden o seu rango de operación, aínda que é posible atopar familias de produtos específicas para certos nichos. Sen embargo, tamén hai dispositivos específicos para tarefas moi concretas, onde os requisitos son tan estritos que ningún outro dispositivo os cumpre. A flexibilidade é completa e non hai restricións para empregar as tecnoloxías máis avanzadas que so estarán dispoñibles en dispositivos comerciais nun futuro próximo.

Case todas as aplicacións de Visión por Computador necesitan afrontar todas etapas de procesamento nun menor ou maior grao. A miúdo, isto conleva aplicar mecanismos que inclúen o manexo do paralelismo espacial (dato), temporal (instrución) e secuencial, ou incluso unha combinación deles. Cada etapa corresponde aproximadamente cun tipo de paralelismo, co que todos estes mecanismos adoitan implementarse na maior parte das aplicacións. As etapas de baixo nivel benefícianse do paralelismo masivo con sistemas de distribución de datos e operacións aritméticas sinxelos. Cando a abstracción aumenta, durante as tarefas de medio nivel, os algoritmos requiren maior información acerca do problema a resolver, polo que se incrementa a súa complexidade. Isto conleva estruturas de datos e fluxos de execución máis complexos, onde a distribución da información fai difícil explotar o paralelismo espacial, aínda que normalmente está presente. As arquitecturas paralelas a nivel de tarefa son capaces de explotar de forma máis eficiente e sinxela esta etapa. As etapas de baixo e medio nivel poden implementarse en solucións hardware puras porque con frecuencia so executan tarefas de cómputo. Sen embargo, a etapa de alto nivel está máis próxima ao software e os enxeñeiros

poden explotar este feito para construír sistemas máis complexos usando un procesador de propósito xeral. Ademais, permitirá actuar como sistema de control das unidades de cómputo ou dos sistemas de comunicación. Isto non está directamente relacionado cos problemas da Visión por Computador pero sen embargo é un requerimento para un prototipo funcional. Neste caso, o uso dun procesador de propósito xeral é un claro beneficio pois facilita enormemente o control e incrementa a flexibilidade do sistema.

A pesar de que é case imposible desenvolver un sistema capaz de executar todas as operacións dun xeito óptimo dada a rica natureza das aplicacións de Visión por Computador, é desexable que proporcione a capacidade para executar calquera operación. O deseño ten que ser escalable para adaptalo ás necesidades específicas de cada aplicación. Deste xeito é posible proporcionar unha familia de dispositivos con diferentes capacidades de cómputo de xeito sinxelo. A arquitectura interna debe ser tamén modular, de modo que desde un esbozo básico se poidan engadir máis características sen cambios dramáticos. En xeral, un microprocesador de alto nivel é un requisito para xestionar comunicacións e operacións complexas entre o sistema e os compoñentes externos do sistema completo. Un certo número de unidades auxiliares capaces de manexar os paradigmas de computación paralelos a nivel de dato e de tarefa executarían a parte máis custosa do algoritmo. En particular, unha unidade de SIMD grande aumentará o rendemento nas primeiras etapas. Un controlador integrado para memorias de alta velocidade é tamén crítico para reducir os problemas de acceso aos datos na memoria externa. Todos estes elementos combinados son capaces de afrontar eficientemente a maioría das situacións que se atopan nos algoritmos máis comunmente empregados.

## Abordando a etapa de baixo nivel

As tarefas da etapa de baixo nivel caracterízanse por ser simples, repetitivas e aplicadas sobre unha gran cantidade de datos, e non requiren unha alta precisión. Sen embargo, son moi custosas computacionalmente, especialmente en sistemas embebidos, o ámbito que se aborda neste traballo.

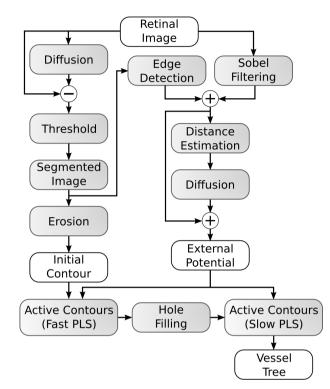

No segundo capítulo preséntase un procesador de propósito xeral para o procesado de imaxes a baixo nivel. En primeiro lugar, preséntase un estudio dunha arquitectura para imaxes binarias (branco e negro), onde se conclúe que o paralelismo espacial masivo non representa a solución máis eficiente. A pesares que a distribución matricial do conxunto de unidades de cómputo con comunicación local entre elas pode explotar moi eficientemente as caracte-

rísticas das tarefas que executan nesta etapa, a correspondencia dun procesador por píxel da imaxe ten varias serias desvantaxes. Por un lado, o número de recursos hardware necesarios é elevado, resultando en procesadores que traballan con imaxes con pouca resolución e con frecuencias de reloxo baixas. A pesares de tratarse de problemas técnicos, o rendemento real e a conveniencia deste tipo de procesadores é menor do esperable teoricamente. Deste xeito, solucións a priori menos óptimas poden superar estas limitacións e ofrecer mellores figuras de mérito.

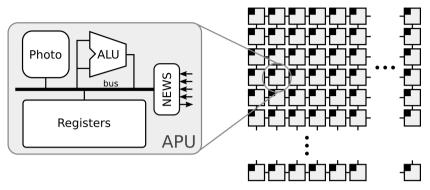

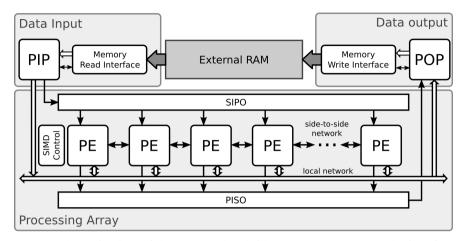

Como resultado, este procesador preliminar foi ampliado para procesar imaxes non binarias, estendendo as capacidades de cada unidade de cómputo e reducindo o paralelismo. Esta arquitectura, unha matriz de procesadores de gran groso, proporciona mellores figuras de mérito. En particular, é máis sinxelo escalar a matriz sen comprometer a frecuencia de reloxo e permite manexar imaxes de maior resolución. Cando se compara con outras propostas, unha implementación en FPGA desta arquitectura mellora os resultados dun procesador SIMD masivamente paralelo que conta con 8500 % máis unidades de cómputo. Esta densidade de integración é acadada empregando arquitecturas de sinal mixta que limitan o tamaño da matriz e a frecuencia de reloxo, limitando a potencia que se pode extraer del. Sen embargo, o consumo de potencia acadado é moi difícil de bater. As matrices masivamente paralelas de procesadores tamén amosan un alto rendemento explotando o paralelismo temporal, aínda que as operacións recursivas reducen en gran medida o rendemento, sendo difícil atopar unha solución de compromiso. O algoritmo empregado para comparar o rendemento e posterior discusión é representativo da súa clase, proporcionando información adicional acerca de como os datos interactúan cando se concatenan os diferentes operadores. Isto danos unha vantaxe durante a etapa de deseño dunha arquitectura especializada en acelerar este tipo de operacións. Os resultados tamén amosan que CPUs convencionais non son eficientes para tarefas de visión temperá, polo que outras aproximacións están claramente xustificadas.

As principais conclusións refírense a como as unidades aritméticas están organizadas e como se distribúen os datos entre elas. Como se víu, unha organización matricial permite afrontar de xeito eficiente operacións de baixo nivel, que inclúen operacións píxel a píxel e interaccións locais. Polo contrario, cando se procesan datos que non son puramente imaxes, unha matriz bidimensional non proporciona a necesaria flexibilidade. Isto acentúase segundo o nivel de abstracción aumenta. A matriz masivamente paralela de procesadores, que explota en gran medida o paralelismo temporal é unha boa proba deste feito. Un problema non resolto polo momento é a entrada e saída de datos. As tarefas de procesado de imaxe normalmente

requiren un gran ancho de banda e unidades de almacenamento de alta capacitade, o que pode limitar o rendemento se as unidades de cómputo están consumindo tempo esperando polos datos a procesar. Superpoñer a transferencia de datos e o seu procesado é esencial.

As conclusións expostas neste capítulo lévannos a propoñer unha versión mellorada da arquitectura inicial, enfocándose en estender o rango de aplicación sen comprometer o rendemento, ampliar os requisitos hardware ou o consumo de potencia.

### Expandindo o rango de operación

O terceiro capítulo amosa unha extensiva optimización da arquitectura proposta no segundo capítulo. A primeira proposta foi deseñada para abordar a etapa de baixo nivel que inclúen a maioría das aplicacións de Visión por Computador, que consumen a maior parte da carga de traballo da CPU. A matriz de procesadores de gran groso probou ser moi eficaz nestas tarefas. Sen embargo, a súa flexibilidade está limitada e non manexa de forma eficiente as posteriores etapas de procesado. A distribución das unidades aritméticas, a representación dos datos e as operacións de entrada/saída non son as adecuadas para as etapas de medio e alto nivel.

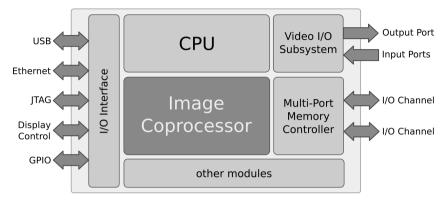

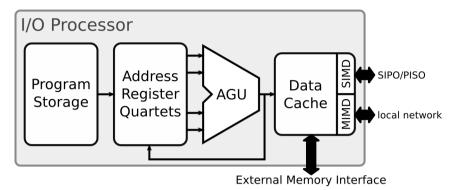

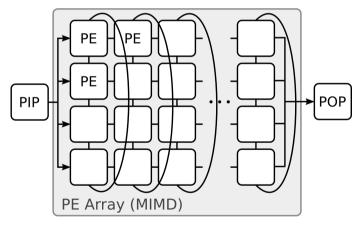

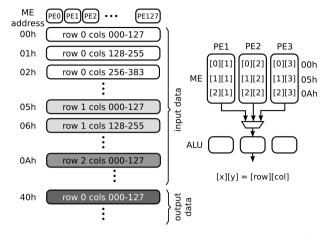

Para deseñar a arquitectura finalmente proposta seleccionáronse as mellores características dos paradigmas de computación SIMD (espacial) e MIMD (temporal), e combináronse para reducir os recursos hardware empregados. Deste xeito, a nova arquitectura pode explotar tanto os paradigmas de computación paralela a nivel espacial e temporal, executando operacións masivamente paralelas en modo SIMD, a nivel de tarefa en modo MIMD e de alto nivel ou de xeito serie nun procesador secuencial. O paradigma de computación pode cambiarse en tempo de execución segundo os requisitos que marque cada un dos algoritmos implementados. O manexo da entrada/saída de datos foi mellorado e permite superpoñer computación e transferencia de datos, reducindo o colo de botella e facilitando o acceso á memoria externa onde se almacenan os datos. Un dos obxectivos desta arquitectura é prover da suficiente flexibilidade como para manexar situacións moi diversas, incluíndo diferentes tipos de datos, tamaños de imaxe ou representacións abstractas. Para este propósito empréganse dúas redes diferentes para intercambiar datos entre as unidades de cómputo. As súas características facilitan a distribución dos datos e reducen o tempo empregado no proceso, aumentando así o rendemento. Ademais da flexibilidade, outro obxectivo perseguido é o de facer a arquitectura altamente configurable, de forma que esta non dependa do número de unidades de cómputo, o tamaño das memorias ou o tipo de operacións aritméticas empregadas. Isto permite crear unha familia de procesadores que aborden diferentes aplicacións en diferentes campos, axustando así non so o rendemento ou o consumo de potencia, se non tamén o custo.

O procesador SIMD/MIMD híbrido foi testeado nun sistema embebido baseado en FPGA. Un conxunto de operadores e algoritmos foi implementado para avaliar o seu rendemento e a súa factibilidade. Os resultados proban que se pode alcanzar un alto rendemento cando os diferentes modos de computación se empregan adecuadamente. A arquitectura foi compara con outras propostas similares, incluíndo a matriz de procesadores de gran groso proposta no segundo capítulo. Os resultados amosan que o prezo a pagar debido ao incremento de hardware e á inclusión de características de cómputo de propósito xeral, que poderían penalizar o rendemento en tarefas específicas, é menor que a ganancia en termos de flexibilidade xa que o rendemento non se ve comprometido.

## Conclusións

Neste traballo, presentouse unha nova arquitectura hardware para acelerar aplicacións de Visión por Computador en sistemas embebidos. Esta arquitectura hardware proporciona un dispositivo dun único chip capaz de executar a maioría dos algoritmos de procesado de imaxe e tarefas relacionadas.

En primeiro lugar introduciuse o problema da Visión por Computador e analizáronse as familias de algoritmos relacionados. Despois de reseñar as súas características, tipo de operacións e complexidade do fluxo de programa, avaliáronse os diferentes paradigmas de computación. Partindo deste coñecemento, propúxose a arquitectura dun procesador masivamente paralelo avaliando a súa viabilidade con tecnoloxía actual. Este procesador incluía un gran número de unidades de cómputo, moi sinxelas, dispostas nunha matriz bidimensional con conexións locais entre eles para intercambiar datos. A pesar de que soamente procesaba imaxes binarias, os resultados amosan que as implementacións prácticas están limitadas a aplicacións que procesan imaxes de baixa resolución e onde o ancho de banda é o maior limitante do sistema. Unha versión posterior deste procesador, estendido para manexar imaxes en escala de grises e a cor, mellora os resultados reducindo o paralelismo pero mellorando as características das unidades de cómputo. Esta arquitectura, como a anterior, prototipouse nunha FPGA para validar as melloras engadidas. Para isto utilizouse un algoritmo que extrae de xeito automático a árbore de veas a partir de imaxes retinianas. Trátase dunha aplicación moi esixente e representativa dos algoritmos de visión temperá, etapa de baixo nivel que o procesador debe

ser capaz de abordar. A arquitectura proposta, unha matriz de procesadores de gran groso, explota o paralelismo de dato dos algoritmos, e foi comparada cunha CPU de propósito xeral, un procesador de plano focal cun esquema dun procesador por píxel, e unha matriz de procesadores masivamente paralela, que explota o paralelismo temporal.

Os resultados obtidos da comparativa das diferentes arquitecturas foi moi valiosa para espandir o rango de operación. Unha das conclusións obtidas é que unha distribución bidimensional das unidades de cómputo non proporciona a suficiente flexibilidade para abordar as etapas posteriores ao baixo nivel. Ademais, explotar o paralelismo a nivel de tarefa non é posible, algo moi importante en gran cantidade de algoritmos incluso aínda que a súa presencia sexa reducida, tal e como amosa a comparativa anterior. Estas conclusións leváronnos a deseñar unha nova arquitectura, baseada na anterior, onde os diferentes módulos permiten reconfigurarse baixo demanda e en tempo de execución.

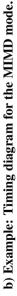

As novas melloras introducidas aumentan a flexibilidade e o rendemento da arquitectura. Deste xeito, é posible configurar dous modos de execución, SIMD e MIMD. No primeiro modo, todos os procesadores executan a mesma instrución. As unidades de cómputo dispóñense nunha matriz unidimensional con conexións locais entre unidades adxacentes. Neste modo, o paralelismo de dato pode ser plenamente explotado empregando a memoria interna que cada unidade aritmética inclúe. Os operadores baseados en ventá, moi importantes nos primeiros pasos de case todos os algoritmos de Visión por Computador, poden implementarse facilmente almacenando varias filas da imaxe de forma adxacente. No modo MIMD, cada unidade de cómputo executa un pequeno programa, unha parte do algoritmo completo. Os diferentes módulos interconéctanse empregando unha rede local programable para reconstruír o fluxo de execución do algoritmo. Este modo explota o paralelismo temporal de forma nativo xa que todas as unidades están traballando de xeito concurrente. A rede autoxestiónase polo que non é preciso incluír control adicional, facilitando a migración de depuración do algoritmo. En ambos modos, dous procesadores independentes controlan a saída e entrada de datos entre as unidades de cómputo e a memoria externa. Isto permite superpoñer a transferencia de datos e o cómputo, incrementando o rendemento global do sistema.

A arquitectura final foi prototipada nunha FPGA e diversos algoritmos foron avaliados para determinar os beneficios que supoñen estas melloras. A pesar de que presenta capacidades de propósito xeral, os resultados mostran que é posible de conseguir un rendemento similar á arquitecturas máis específicas, como a presentada no capítulo segundo, sendo posible aumentar de xeito considerable a flexibilidade sen comprometer o rendemento.

### Traballo futuro

A arquitectura proposta neste traballo proporciona unha base sólida sobre a cal é posible engadir novas características para aumentar a súa flexibilidade e rendemento, entre outras figuras de mérito. En particular e baseado nos resultados obtidos, unha arquitectura multi-núcleo proporcionará melloras importantes. Para executar simultaneamente ambos paradigmas de computación, SIMD e MIMD, unha interconexión interna para transferir os datos entre os diversos núcleos é máis interesante que aumentar o número de unidades de cómputo mantendo un so chip.

Máis aló de modificacións estruturais e implementacións baseadas en FPGAs, a arquitectura foi concibida para implementarse en ASICs. A arquitectura pode ser optimizada a un nivel máis profundo, especialmente o apartado referente ás unidades aritméticas, restrinxidas en capacidade debido á limitación dos recursos dispoñibles na FPGA. Isto abre novas direccións de investigación e permite avaliar de xeito máis preciso parámetros como o consumo de potencia ou os requisitos de área.

## Introduction

## Motivation and objectives

Computer Vision algorithms and techniques are increasingly robust and accurate, offering new possibilities for the treatment of visual information. However, this entails an increasing in the computing requirements, and their implementation on devices beyond the scope of the prototypes is becoming more complex. Novel approaches are required in order not to trim the characteristics of the algorithms and to meet the different trade-offs such as speed, latency, power consumption or cost. This includes both hardware architectures and software techniques to fully exploit the computing capabilities of the target device and to take advantage of the characteristics of the algorithms.

For a given Computer Vision problem there are many different techniques and approaches proposed in the literature. The variety of algorithms is very broad and they present very different characteristics, including not only data representation or arithmetic operations but also different computing paradigms and program complexity. This makes the design of the hardware devices very challenging if the same architecture has to face different algorithms with tight constraints.

Desktop computers are often employed to develop the algorithms. They offer large flexibility to run any algorithm and evaluate its feasibility and accuracy. However, the target device is application-dependent and supplementary hardware modules are frequently used to speed-up the computation. In order to meet the requirements of the application, a custom architecture may be a need. In this case, all figures of merit are likely to be optimized. There are many different fields where the different trade-offs are more or less important so the different architectures have to deal with different restrictions. The advances in the semiconductor industry enable embedding more and more resources in the same unit of area while maintaining a restrained power consumption. This have made possible to develop new embedded processors with similar performance to recent-past conventional systems. This way, new applications are now technically feasible and the importance of the embedded vision market is increasing significantly. Custom systems-on-chip enable to embed on the same chip all the necessary modules for a given system, including computing, control and communication, providing a significant advantage over equivalent multi-chip systems. However, custom systems-on-chip require a long period of design and many resources, human and materials. In addition, custom hardware also requires a training period by the software engineers to fully exploit the capabilities of the hardware, reducing the competitive advantage of these systems. This becomes critical as the number of specific units grows to face the different algorithms employed to solve the Computer Vision problem.

The objective of this work is to provide a single-chip architecture able to run most of the Computer Vision algorithms with adaptive performance on the critical steps of the algorithms. In addition, it must be able to run all the other steps so that the overall performance is not compromised. The architecture also aims to reduce the time spent in migrating the algorithms, reducing the mapping stage by easing algorithm parallelization and synchronization between the different concurrent kernels of the algorithm. From the flexibility point of view, the system has to be modular and scalable in order to address different targets on the market and meet different trade-offs such as performance, area or cost. Architectural improvements and custom modifications must be done easily without dramatically change the way the hardware works. All these elements combined will provide enough flexibility and performance in order to run efficiently many different Computer Vision algorithms, with the benefit of employing a single device.

## Contributions

The primary contributions of this dissertation are:

An analysis of how representative and conceptually different hardware architectures implement diverse Computer Vision algorithms by taking advantage of their mathematical operations and dataflow.

- An architecture for low-level and early vision image processing which solve a number of technical problems found on existing devices, expanding its range of operation, flexibility, accuracy, cost and development times.

- A modular and scalable architecture for embedded Computer Vision systems, which focus on easing algorithm migration by natively parallelize the processing threads and data transfer. This architecture features general-purpose capabilities and dynamically reconfiguration at runtime to adapt the internal datapath according to the operations of the algorithm it is running.

- A demonstration and evaluation of the potential value of reconfigurable datapaths to face complex operations, beyond the Computer Vision field.

These contributions can be found in the publications listed below:

- SIMD Array on FPGA for B/W Image Processing. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in 11th International workshop on Cellular Neural Networks and their Applications (CNNA 2008).

- SIMD and Cellular Neural Networks as Fine-Grained Parallel Solutions for Early vision on FPGAs. Alejandro Manuel Nieto Lareo, Natalia F., Jordi A.C., J. Riera, Víctor Manuel Brea Sánchez and David López Vilariño, in 23th Conference on Design of Circuits and Integrated Systems (DCIS 2008).

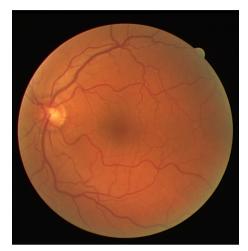

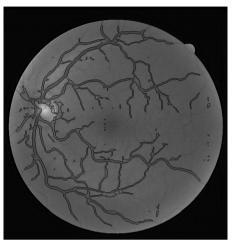

- A Digital Cellular-Based System for Retinal Vessel-Tree Extraction. César R., Alejandro Manuel Nieto Lareo, Roberto O., Víctor Manuel Brea Sánchez and David López Vilariño, in 19th European Conference on Circuit Theory and Design (ECCTD 2009).

- On-Chip Retinal Image Processing: Performance Analysis on Different Approaches. Alejandro Manuel Nieto Lareo, Roberto O., Víctor Manuel Brea Sánchez and David López Vilariño, in 24th Conference on Design of Circuits and Integrated Systems (DCIS 2009).

- An FPGA-based Topographic Computer for Binary Image Processing. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in *Image Processing (In-Tech Education and Publishing, 2009).*

- FPGA-Accelerated Retinal Vessel-Tree Extraction. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in 19th International Conference on Field Programmable Logic and Applications (FPL 2009).

- Performance analysis of massively parallel hardware architectures for medical image processing. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in Eurasip Journal on Image and Video Processing - Special Issue on Real-Time Image Processing on Multi-Cores, Many-Cores and High-level FPGA-based Platforms (2011).

- Towards the optimal hardware architecture for Computer Vision. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in *Machine Vision* (*In-Tech Education and Publishing, 2011*).

- Feature detection and matching on an SIMD/MIMD hybrid embedded processor. Alejandro Manuel Nieto Lareo, David López Vilariño and Víctor Manuel Brea Sánchez, in 8th IEEE Workshop on Embedded Vision (EVW 2012).

- SIMD/MIMD dynamically-reconfigurable architecture for high-performance embedded vision systems. Alejandro Manuel Nieto Lareo, Víctor Manuel Brea Sánchez and David López Vilariño, in 23rd IEEE International Conference on Applicationspecific Systems, Architectures and Processors (ASAP 2012).

The results of this work are also reflected in the following patent:

• Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión. Alejandro Manuel Nieto Lareo, David López Vilariño and Víctor Manuel Brea Sánchez. *Patent Application Number P201101381, Spain (December 30th, 2011).*

## Outline

This thesis is divided in three chapters. Chapter 1 introduces the challenges of Computer Vision. The different computing paradigms and hardware architectures and devices to face the algorithms requirements are also reviewed. In Chapter 2, a new hardware architecture for early vision processing is presented. After examining different approaches, a study of a

massively parallel processor for binary image processing is carried out. The conclusions of the study are essential for the design of a more efficient and capable architecture for generalpurpose early vision processing, which is extensively tested employing a highly computationally consuming algorithm employed in medical applications. In Chapter 3, the results of the comparison of the general-purpose early vision processor are employed to define a new and enhanced architecture. This architecture is intended for embedded devices and focuses on dynamic reconfiguration to reproduce the algorithm's dataflow. This way, the architecture increases its range of operation so that all steps of a general Computer Vision algorithm can be performed efficiently by the embedded device. The results of implementing several common image processing algorithms and a comparison with similar approaches complete this chapter. Finally, the main conclusions of this thesis are conveyed.

## CHAPTER 1

## **BACKGROUND AND RELATED WORK**

Computer Vision systems are experiencing a large increase in both range of applications and market sales [1]. From industry to entertainment, Computer Vision systems are becoming more and more important and the research community is making a big effort to make them able to handle complex scenes focusing on the accuracy and the robustness of the results. The new algorithms enable more advanced and comprehensive analysis of the images, expanding the set of tools to implement these applications [2].

Although there are new algorithms available to approach sophisticated new applications with a high degree of accuracy, not all the algorithms are adequate to be deployed in industrial systems. Parameters like power consumption, integration with other system modules, cost and performance limit the range of suitable platforms. In most cases, the algorithms must be adapted to achieve a trade-off solution and to take advantage of the selected platform.

Conventional systems like PCs or GPUs are increasingly improving performance and including more features but their use is limited to areas where portability, power consumption and integration are not critical. When the algorithm is highly complex, with an irregular execution flow, complex data representation and elaborated patterns to access to data, a significant gain is not achieved when moving the algorithm to an *ad hoc* hardware design. In this case, a high-end CPU and a GPU with support for GPGPU is a flexible and very powerful combination that will outperform other choices [3].

However, when a conventional system does not meet the requirements of the application, a more ambitious planning is needed. For instance, migrating the algorithm to a dedicated device such as a DSP, an FPGA or a custom chip [4]. At this point, the designers have to

consider alternatives as to reduce operating range, accuracy and robustness of the results, or to remove expensive operations in order to simplify the hardware that will be implemented [5]. Otherwise, a significant improvement will not be achieved. PC-based systems enable a great flexibility at cost of performance, so pure software-based algorithms hardly match pure hardware implementations. This is a serious limitation because it can compromise the efficiency of the application. This is the reason why the industry is making great efforts to develop novel architectures that enable greater flexibility to adapt the algorithms without compromising the quality of the results.

Computer Vision applications are often divided into several stages depending on the abstraction level and thus in the complexity of the operations. Initially, operations are quite simple and repetitive but applied over a large set of data with a very reduced data dependent program flow, so massive parallelism is essential for performance. Then, the level of abstraction increases, resulting in more complex algorithms. Temporal and task parallelism is key as the data set is smaller and the program flow is often data-dependent. Finally, the system output has to be determined, performing high level operations over complex data representations but reduced data sets and with higher precision as usual requirement. An efficient Computer Vision system must deal with all these stages. The selection of the computation model will determine the performance of the device in each one of the stages. According to Flynn's Taxonomy [6], paradigms can be classified into four categories based on the number of instructions and data streams processed simultaneously. So, which is the optimal paradigm for such applications? Increase the number of concurrent instructions? Increase the number of data elements processed simultaneously? A combination of both?

Taking into account the application requirements, a suitable platform to build the system must be selected. Besides general parameters (performance, cost and integration), there is a set of factors that restrict the computing paradigms and the devices that can be selected. For instance, a critical parameter is the way the data are transferred to the device because I/O operations are one of the bottlenecks in high-performance systems. Data type (integer, fixed-point or floating-point) and representation will affect the computational units. The program flow will constrain the inner connections between these units and the storage elements. To tackle these and other parameters, a careful analysis of the state-of-the-art of the algorithms has to be made.

This chapter addresses a review of different computing paradigms and platforms oriented to image processing. In addition, a representative set of Computer Vision algorithms covering the three levels of processing is evaluated. This study will allow us to observe the algorithms based on a set of common characteristics: operations, data type, program flow, etc. This is critical to design new hardware architectures in order to maximize performance. The analysis from the hardware point of view will highlight the best features of the most used computing paradigms in order to establish a relationship between the type of operation, data, programming model and hardware architecture. An efficient architecture for Computer Vision must combine all the selected features. The analysis of the characteristics of the different algorithms will lead us to an optimized general-purpose hardware architecture for Computer Vision.

## 1.1 The challenges of Computer Vision

Traditionally, Computer Vision (CV) applications include building blocks from three computation levels: low-, mid- and high-level vision computing. The type of operations, the data representation and the flow execution of programs depend deeply on the considered level of this hierarchy. Nevertheless, current CV-algorithms are composed of many different processing steps regarding the type of data and the way these are computed, which makes difficult to classify them only in one subgroup. Following, a rather rough classification of widely used CV-algorithms is made, keeping in mind the data domain and the complexity of the involved operations.

### 1.1.1 Low-level vision

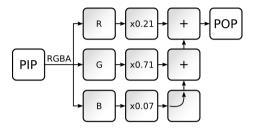

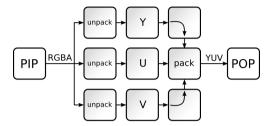

After image acquisition, some preprocessing steps are often required. These are intended to provide reliable input data for subsequent computing stages. Some typical operations are noise reduction, color balancing, geometrical transformation, etc. Most of these operations are based on point or near-neighborhood operations. Point operations are performed at pixel-level in such a way that the output only depends on the value of any individual pixels from one or several input images. With this type of operation it is possible to modify the pixel intensity to enhance parts of the image, by increasing contrast or brightness. Equally, simple pixel-to-pixel arithmetic and Boolean operations also enable the construction of operators as *alpha blending*, for image combination or color space conversion. Neighborhood operations take also into account the value of adjacent pixels. This operation type is the basis of filtering, binary morphology or geometric transformation. They are characterized by simple operations, typically combining weighted sums, Boolean and thresholding processing steps.

After preprocessing stages, useful information has to be extracted from the resulting images. Common operations are edge detection, feature extraction or image segmentation. Edges are usually defined as step discontinuities in the image signal so finding local maxima in the derivative of the image or zero-crossings in the second derivative are suitable to detect boundaries. Both tasks are usually performed by the convolution of the input image with spatial filtering masks that approximate a first or second derivative operator.

Feature points are widely used for subsequent computing steps in multiple CV-applications. Basically, a feature represents a point in the image which differs from its neighborhood. One of the benefits of local features is the robustness against occlusion and the ability to manage geometric deformations between images when dealing with viewpoint changes. In addition, they improve accuracy when, in the same scene, objects are at different planes, (i.e. at different scales). One of the most popular techniques is that proposed by Harris [7] to detect corners. It is widely used due to its strong invariance to rotation, image noise and no large illumination changes. It uses the local auto-correlation function, which describes the gradient distribution in a local neighborhood of each image point to detect the location of the corners. Using the locally averaged moment matrix from the image gradients, corners will be located at the maximum values. Another frequently used technique is the Scale-Invariant Feature Transform (SIFT) [8]. SIFT localizes extrema both in space and scale. Using the Difference of Gaussians as scale-space function, the images are filtered with Gaussian kernels of different sizes (scales). This is performed for different image sizes (octaves). The response of each filter is subtracted from the immediately following in the same octave. The interest points are scale-space extrema so local maxima and minima are extracted by comparing the neighborhood points in the same, the previous and the subsequent scales. To improve accuracy, a sub-pixel approximation step is done, interpolating the location of the feature inside the scale-space structure. The number of octaves and scales can be tuned to meet the system requirements. SIFT provides invariance against scale, orientation and affine distortion, as well as partial occlusion and illumination changes. Other algorithms were proposed to improve accuracy or performance like, the Speeded Up Robust Features (SURF) [9] or the Gradient Location and Orientation Histogram (GLOH) [10]. This kind of detectors are quite complex and their performance can be low even using custom hardware. For this reason, less reliable algorithms are still in use, as Harris Corner Detector, FAST [11] or the Smallest Univalue Segment Assimilating Nucleus (SUSAN) [12] corner detectors. In this sense, techniques such as [13] provide a framework for very fast feature detection and matching.

Segmentation refers to the process of separating the data into several sets according to certain characteristics. There are several techniques to carry out this task, either based on boundaries or regions [14] [15]. Nevertheless, most of them rely on near-neighborhood operations. Particular attention deserves the clustering methods like the popular k-means which partitions the data set into several clusters according to a proximity criterion defined by a distance function. These methods are not restricted to image data. N-dimensional sets of abstract data can also be partitioned. Furthermore, information about the scene or domain can be introduced (number and characteristics of the target clusters). Therefore, they might be classified either as a low or mid-level vision stage.

#### 1.1.2 Mid-level vision

Mid-level CV stages usually operate on images from previous processing steps, often binary images, and produce a lower amount of data but with a higher concentration of information. Some common operations are object classification and scene reconstruction.

One of the goals of Computer Vision is to recognize objects in a scene. Based on object location, pose or 2D/3D spatial relations between the objects, the algorithms have to be able to analyze the scene and its content. This involves issues such as dealing with object models, classifiers and the ability to integrate new information in the models. In the literature, a large amount of techniques can be found, usually classified as global methods, more intended for object detection and local feature-based methods for object recognition. In all of them good image registration is essential for both accuracy and performance [16]. As for the global methods, common techniques are based on *template-based matching*, which employs a convolution mask or template to measure the similarity between an object patch and the template. In this sense, normalized cross-correlation (NCC), sum of squared differences (SSD) or sum of absolute differences (SAD) are widely used. As for local methods, local feature descriptors play an important role. Roughly speaking, a descriptor is an abstract characterization of a feature point based on its environment. One of the most popular techniques is the proposed in second part of the SIFT algorithm based on stacked orientation histograms which associate a high dimension vector to each keypoint. In order to reduce the amount of false positives and negatives during the matching stage the search area is limited by using strategies like the nearest neighbor search (NNS) which attempts to find the nearest points of a given one in a vector space. An *indexing structure* allows to search for features near a given feature rapidly. This is the case of the *K*-dimensional trees, which organize points in a k-dimensional space in such a way that each node has at most two child nodes.

Scene reconstruction consists of the generation of scene models starting from their components. There are different techniques to reconstruct one or several objects in a scene. To build a 3D model, coordinates of scene points have to be calculated from the objects. If the location of the camera is known, 3D coordinates of a scene point can be determined from its projection on image planes of different viewpoints. The whole process starts with feature extraction and matching. Using geometric consistency tests it is possible to eliminate wrong matches. There are different solutions to estimate the fundamental matrix, as the *RANdom SAmple Consensus* (RANSAC). Once the matches between images are consistent, camera pose and scene geometry is reconstructed using *Structure from Motion* methods and refined with *Bundle adjustment* techniques [17].

#### 1.1.3 High-level vision

The high-level stage often starts from an abstract representation of the information. This stage is highly application-dependent, but due to the variety of operations, data structures, memory access patterns and program flow characteristics are often only compatible with a general purpose processor. High-level processing is characterized by the use of a small set of data to represent knowledge about the application domain. More complex data structures are needed to store and process this information efficiently, making the operations and the memory access patterns more elaborated. This, together with the inherent complexity of decision making, makes the program flow very variable.

Robust pattern recognition, object identification, complex decision making or system adaptation are some of the benefits of integrating Artificial Intelligence methods with Computer Vision. Otherwise, the system would be limited to a predetermined set of actions. Machine learning makes computers capable of improving automatically with experience. This way it is possible to generalize the behavior from unstructured information with techniques such as neural networks, decision trees, genetic algorithms, regression models or support vector machines. Machine learning has emerged as a key component of intelligent computer vision systems, contributing to a better understanding of complex images [18] [19].

Data mining is the process of analyzing data using a set of statistical techniques in order to summarize into segments of useful information. This makes possible analyze data from different dimensions or angles, categorizing and summarizing the identified relationships, making

evident hidden relationships or patterns between events. Contrary to Machine learning, data mining focuses on discovering hidden patterns instead of generalizing known patterns using the new data.

It is very difficult to establish a classification of tasks and operations for high-level processing. Some of the performed tasks fall within the scope of the measurement of application specific parameters such as size and pose of objects, fault detection and monitoring specific events such as traffic situations, for example. The algorithms and technologies are very diverse and most of them lie in statistical analysis and artificial intelligence domains.

As it was previously mentioned some tasks that initially fit into the low or medium level stages due to its context actually are more like high-level operations by the type of operations performed. This is related with the commonly used bottom-up image analysis, which starts from raw data to extend the knowledge of the scene. However, new approaches include feedback to perform top-down analysis. This way, low- and mid-level stages can be controlled with general knowledge of the image, improving the results.

# 1.2 Computing platforms

Given the wide range of algorithms and applications of Computer Vision, it is clear that it does not exist a unique computing paradigm or an optimal hardware platform. The type of operations, the complexity of data structures and especially the data access patterns greatly determine parameters such as the range of application, performance, power consumption or cost. This section presents some of the most prominent platforms in image processing, focusing on their strengths and weaknesses.

## 1.2.1 Computing paradigms

The Flynn's taxonomy [6] classifies the computer architectures in four big groups according to the number of concurrent instructions and data sets processed. Image processing tasks perform more or less efficiently depending on the selected paradigm. In order to develop a Computer Vision application it is crucial to exploit the spatial (data) or temporal (task) parallelism to meet trade-offs among performance, power consumption or cost.

#### SISD

*Single Instruction Single Data* (SISD) refers to the conventional computing model. A single processing unit executes a sequence of instructions on a unique data stream. Most modern computers are placed under this category and, although only one processor and one memory element are present, those which are able to pipeline their data-path are generally classified under the SISD category as they are still *serial computers*.

This paradigm performs better when spatial and temporal parallelism are hard to exploit. As seen previously, high-level image processing fits the SISD paradigm because most tasks are sequential, with a complex program flow and strong dependences between data. As processing is done sequentially, most optimizations aims to enhance the access between the memory and the arithmetic unit. Memory and processor speed are the main constraints. Furthermore, some kind of parallelism can be exploited when pipelining the data-path. Data allocation, pre-fetching and reducing stalls in the pipeline are some of the possible optimizations.

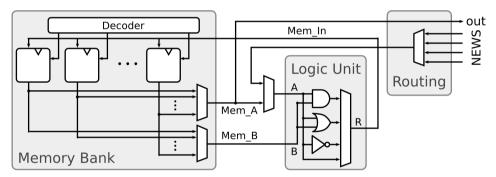

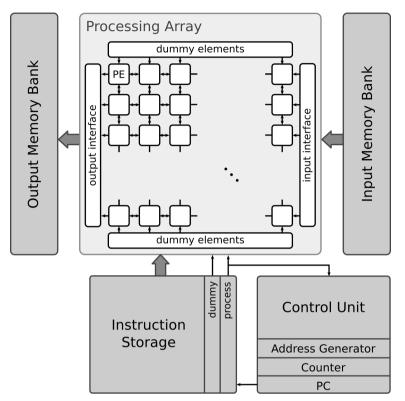

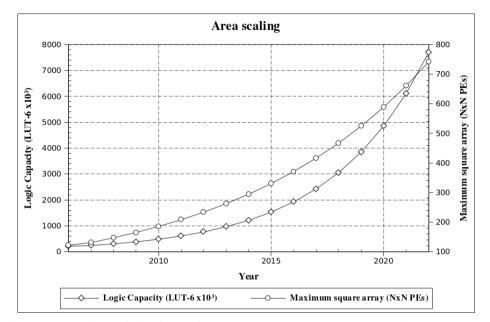

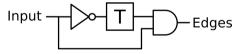

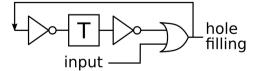

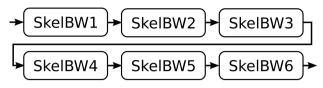

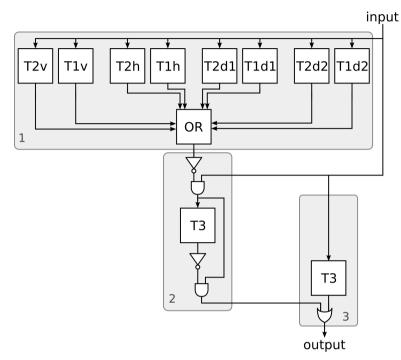

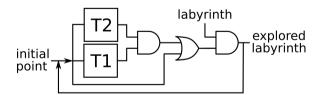

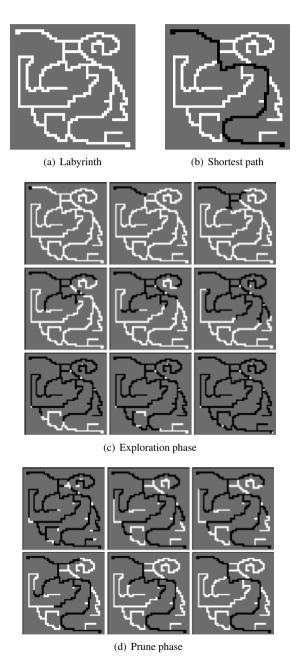

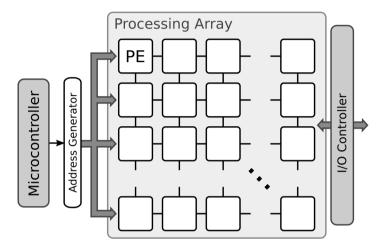

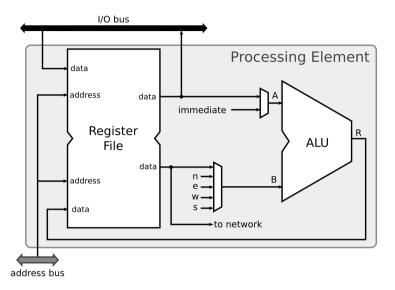

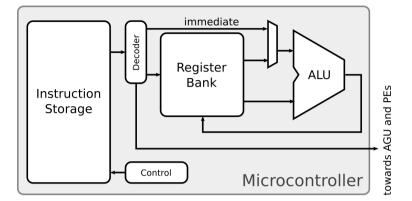

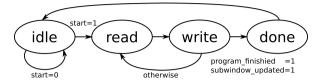

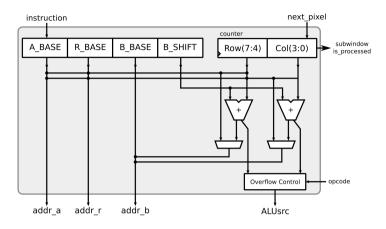

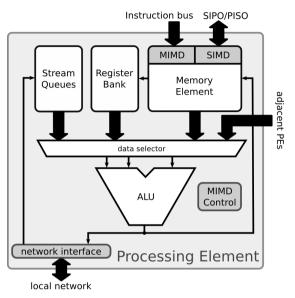

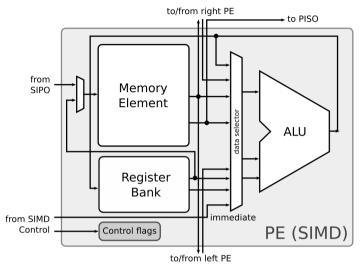

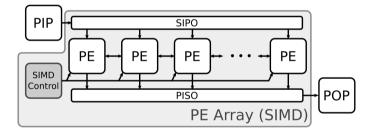

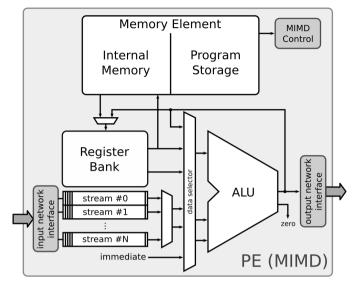

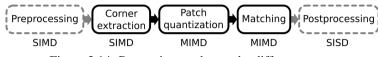

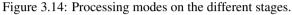

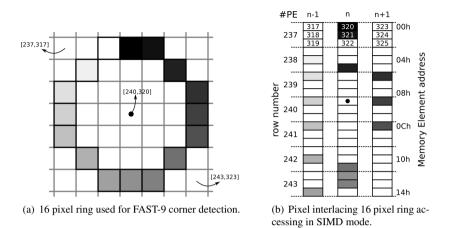

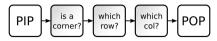

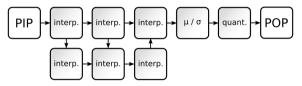

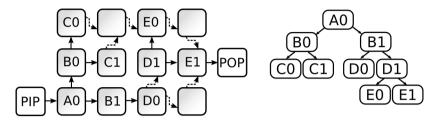

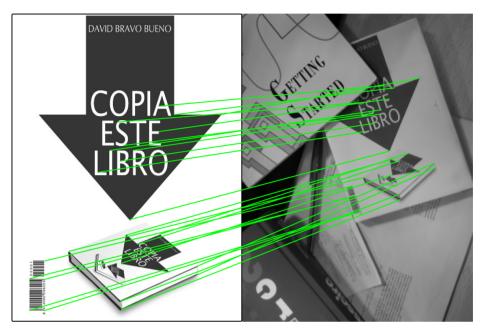

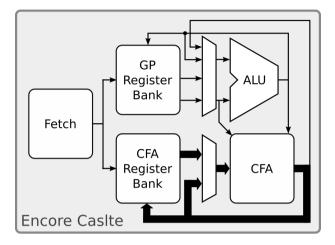

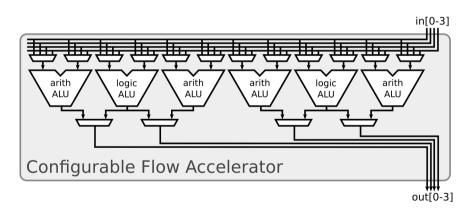

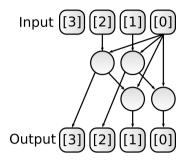

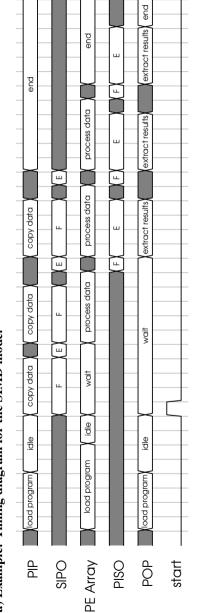

## SIMD