Feature detectors are a category of algorithms in computer vision intended for applications such as visual tracking, object recognition or segmentation. Invariance against illumination levels, partial occlusions or geometrical transformations as rotations or scaling are key issues in the design of a high quality feature detector.

The invariance against scaling in feature detectors like Scale Invariant Feature Transform (SIFT) is achieved with the so called Gaussian pyramid. The Gaussian pyramid comprises a set of octaves. Each octave is an image of half resolution of the former octave. In turn, every octave contains a set of scales. The scales are built up by filtering with Gaussian filters of increasing width or sigma levels.

The construction of the Gaussian pyramid demands high computational time. A dedicated CMOS chip which incorporates image acquisition is a good approach to reach fast and power-efficient image analysis.

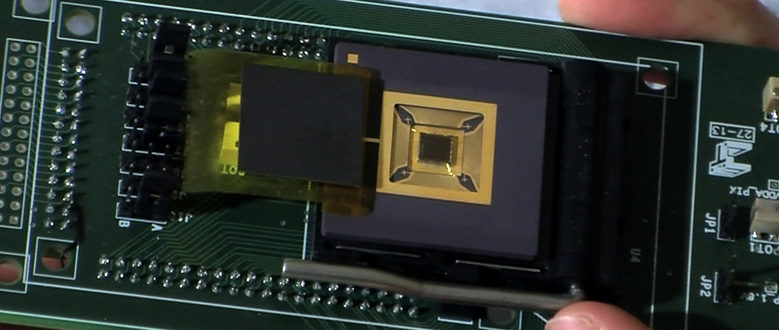

This demo will include real-time tests of a proof of concept CMOS vision chip on standard 180 nm technology that performs the Gaussian pyramid. The chip captures an image of 176 x 120 px. It also performs the Gaussian pyramid with a switched capacitor network in a double Euler configuration. The area of the chip amounts to 5 x 5 mm². The photosensors are nwell photodiodes in a 3 Transistor Active Pixel Configuration (3T-APS) occupying 7.4 x 6.7 um². Groups of 4 photodiodes are arranged in Processing Elements (PEs). The PEs contain local circuitry for analog to digital conversion and correlated double sampling. The chip provides the Gaussian pyramid of 3 octaves and 6 scales each with an energy cost of 26.5 nJ at 2.64 Mpx/s with an RMSE when compared to a pure software solution running on a PC below 1.2% of full scale value.

Authors

-

- Researchers

- Víctor Manuel Brea Sánchez

- Manuel Suárez Cambre